RAM

Version vom 13. Februar 2018, 10:22 Uhr von Janning (Diskussion | Beiträge)

Definitionen

Arbeitsspeicher

- Im Arbeitsspeicher werden vom Prozessor zu verarbeitende Daten zwischengespeichert. Im Gegensatz zu einer Festplatte, welche diese Aufgabe theoretisch ebenfalls übernehmen könnte, gehen hier jedoch die Daten nach entfernen der Stromversorgung verloren. Man spricht hier auch von flüchtigem Speicher. Dafür erreicht jedoch Arbeitsspeicher eine wesentlich höhere Geschwindigkeit.

RAM

- Der RAM (Random Access Memory) ist ein Speichertyp, der aus einzellnen Zellen besteht und zufällig beschrieben wird. Diese Speicherzellen werden durch eine Speicheraddresse angesprochen und können so Informationen aufnehmen.

Arten von RAM

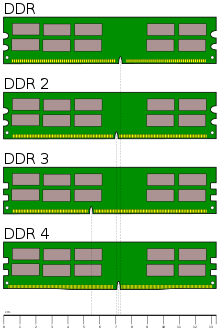

- SDRAM (Synchronous Dynamic Random Access Memory) erkennt man unten an den zwei Zacken.Bis zum ersten Zacken beträgt es genau 2cm.Vom ersten Zacken bis zur Kerbe beträgt es 4cm.

- DDR (SD-)RAM (Double Data Rate Synchronous Dynamic Random Access Memory) erkennt man unten an dem einen Zacken unten ,man erkennt es auch an den zwei Zacken auf der Seite.Der Abstand beträgt von der linken bis zur Kerbe exact 7,2cm.

- DDR2 (SD-)RAM erkennt man an den zwei Zacken an der Seite.Man erkennt es auch an dem:Von der liken Seite bis zur Kerbe sind es 7cm.

- DDR3 (SD-)RAM erkennt man an dem:Von der linken Seite bis zur Kerbe sind es 5,5cm.

- DDR4 (SD-)RAM erkennt man an dem:Von der linken Seite bis zur Kerbe sind es 7,1cm.

Latenzzeiten

- CAS: Der Parameter Column Address Select wird bei der Adressierung der Speicherzelle für die Spalte übertragen. Die angegebene Kennziffer gibt dabei die Anzahl der Taktzyklen (Verzögerungszeit) an, die vom Absenden bis zur Umsetzung des Befehls benötigt werden.

- TRCD: Der Parameter Time Row-to-Column Delay beschreibt bei einem DRAM die Zeit, die nach der Aktivierung der Wortleitung verstrichen sein muss, bevor ein Lesekommando gesendet werden darf.

- TRP: Der Parameter Time Row Precharge beschreibt die Zeit, die nach dem Kommando Vorladen (PreCharge) als Minimum verstrichen sein muss, bevor ein erneutes Kommando zur Aktivierung einer Zeile in der gleichen Bank gesendet werden darf.

- tRAS: Das time Row Access Strobe Signal adressiert dabei die Zeile der Speicherzelle und die Kennziffer gibt dabei an, wie viele Taktzyklen dafür verstrichen sein müssen, bevor das Kommando zum Deaktivieren der Zeile gesendet werden darf.

Berechnung

- Latenzzeit (in ns) = ( 2 * Timing ) / effektive Takt * 1000

Beispiele

- DDR2-667 CL 4-4-4-12

- CAS: Latenzzeit = ( 2 * 4 ) / 667 MHz * 1000 = 11,99ns ~ 12ns

- TRCD: Latenzzeit = ( 2 * 4 ) / 667 MHz * 1000 = 11,99ns ~ 12ns

- TRP: Latenzzeit = ( 2 * 4 ) / 667 MHz * 1000 = 11,99ns ~ 12ns

- tRAS: Latenzzeit = ( 2 * 12 ) / 667 MHz * 1000 = 35,98ns ~ 36ns

- DDR3-1600 CL 8-8-8-24

- CAS: Latenzzeit = ( 2 * 8 ) / 1600 MHz * 1000 = 10ns

- TRCD: Latenzzeit = ( 2 * 8 ) / 1600 MHz * 1000 = 10ns

- TRP: Latenzzeit = ( 2 * 8 ) / 1600 MHz * 1000 = 10ns

- tRAS: Latenzzeit = ( 2 * 24 ) / 1600 MHz * 1000 = 30ns

Paritätsprüfung

- Die Paritätsprüfung ist ein Sicherheitsfeature bei dem sowohl die Daten auf ihre Vollständigkeit/Richtigkeit als auch der Speicher auf seine Funktion überprüft werden können. Dabei wird neben den Datenbytes auch ein zusätzliches Bit, das sogenannte Paritätsbit abgespeichert. Für das erneute Prüfen und einstellen dieses Paritätsbits stehen zwei Verfahren zur Verfügung. Bei beiden Verfahren wird das Datenbyte auf seine Anzahl an enthaltenen Einsen geprüft, welche gerade oder ungerade sein kann, und anschließend das Paritätsbit auf "1" für "OK" oder "0" für "Paritätsfehler" gesetzt.

- ungerade Parität: Auch Parity-Odd genannt. Hier ist eine ungerade Anzahl an Einsen im Datenbyte gewünscht und führt dazu, dass das Paritätsbit auf "0" für "OK" gesetzt wird. Umgekehrt führt hier eine gerade Anzahl zu einem Paritätsfehler (Paritätsbit auf "1" gesetzt).

- gerade Parität: Auch Parity-Even genannt. Hier ist eine gerade Anzahl an Einsen im Datenbyte gewünscht und führt dazu, dass das Paritätsbit auf "0" für "OK" gesetzt wird. Umgekehrt führt hier eine ungerade Anzahl zu einem Paritätsfehler (Paritätsbit auf "1" gesetzt).

ECC - Speicher

- Um bei einem Speicher eine Datenintegrität zu gewährleisten, kann mit Hilfe des ECC Error Correction Code (Fehlerkorrekturcode) ein Fehler ermittelt und anschließend korrigiert werden. Sollte ECC einen Fehler mit mehr als 1 Bit identifiziert haben (In mehr als einem Datensatz steht das Paritätsbit auf "1"), wird ein Paritätsfehler gemeldet und anschließend selbstständig korrigiert. ECC-Speicher sind bedingt durch die Herstellung recht teuer und werden daher überwiegend nur in Servern und High-End-PCs eingesetzt. Damit der ECC-Speicher verwenden kann, muss der Computer über eine Unterstützung (BIOS-Einstellung und/oder Controllerbaustein) verfügen.